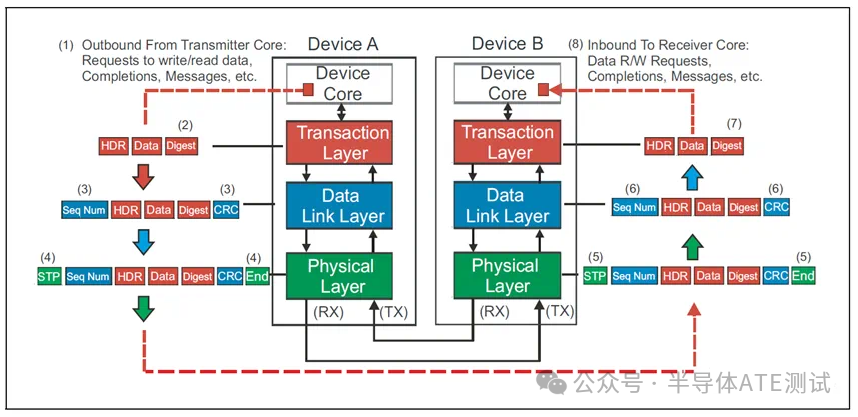

在数字化时代,数据的高速传输如同城市的交通网络,而PCIe(Peripheral Component Interconnect Express) 正是这条“高速公路”的核心基石。从显卡到固态硬盘(SSD),从AI加速卡到5G基站,PCIe凭借其高带宽、低延迟和可扩展性,成为连接计算设备的关键技术。然而,PCIe的卓越性能背后,是一套复杂的协议体系、严格的硬件设计规范以及精密的生产测试流程。PCIe系列文章将与您一起探索PCIe的六大核心领域: 1. PCIe协议通信原理——如何实现高效数据传输? 2. Gen3协议浅析——128b/130b编码如何提升效率? 3. ATE测试揭秘——如何确保每一块PCIe设备的可靠性? 4. PAM4测试挑战——高速信号如何应对噪声与抖动? 5. Ball Map布局艺术——芯片封装如何优化信号完整性? 6. PCB设计黄金法则——如何避免信号衰减和串扰? 望能揭开PCIe技术的神秘面纱,深入浅出了解PCIe 协议应用,展现其背后的科学与工程之美。 一. PCIe协议通信原理、主要PIN脚功能及与其他通信协议对比 PCIe协议采用分层设计(类似OSI模型) · 事务层(Transaction Layer):处理TLP(事务层封包)的打包/拆包,包括读写请求、配置周期,事务排序等。 · 数据链路层(Data Link Layer):DLLP生成/解析,负责错误检测(CRC)、ACK/NACK流控,确保数据可靠性。 · 物理层(Physical Layer):有续集(Ordered Sets)生成/解析,处理电气信号、时钟恢复、串并转换 8b/10(Gen1/2)编码解码或128b/130b(Gen3/4/5)编码解码编码等。 PCIe 协议三层结构就像快递公司,作为老板的事务层决定发什么数据(读/写/配置)并将需要发出的包裹打包成TLP,物流主管-数据链路则需要给TLP添加序列号(快递单号),CRC防伪码(以防包裹被调包),发现丢件就要求重发(NAK机制),货车司机-物理层 负责吧数据变成差分电信号,根据集装箱规格采用不同的编码模式压缩装箱,飞驰在传输线上,以确保每个比特按时送到显卡,固态硬盘等用户手中。

|

| 引脚类型 | 功能描述 |

| PERST# | 全局复位信号(低电平有效) |

| REFCLK+/REFCLK- | 参考时钟(100MHz差分信号),用于同步通信 |

| TX+/TX- | 发送差分信号对(设备→主机) |

| RX+/RX- | 接收差分信号对(主机→设备) |

| PRSNT# | 热插拔检测引脚,指示设备是否存在 |

| WAKE# | 唤醒信号,用于低功耗状态唤醒 |

| SMCLK/SMDAT | 系统管理总线(SMBus)引脚,用于设备配置和温度监控 |

| JTAG* | 可选引脚,用于调试(TCK/TMS/TDI/TDO) |

注:PCIe插槽还包含电源引脚(+3.3V、+12V)和接地引脚(GND)。

PCIe与其他常用通信协议对比

| 协议 | 拓扑结构 | 传输方式 | 带宽(典型值) | 应用场景 | 优势 | 劣势 |

| PCIe | 点对点 | 差分双向串行单工 | 3.0 x16: 16GB/s | 高速外设(GPU,SSD) | 高带宽低延迟可扩展性强 | 引脚较多成本较高 |

| USB | 星型/树型 | 差分双向串行单工(USB2.0)双工(USB3.0+) | USB4: 40Gbps | 通用外设(键鼠、存储) | 热插拔通用性强 | 协议开销大延迟较高 |

| SATA | 点对点 | 差分双向串行双工 | SATA III: 6Gbps | 存储设备(HDD/SSD) | 简单低功耗 | 带宽受限无法扩展 |

| I2C | 总线型 | 单端同步双向串行半双工(SDA分时复用) | 3.4Mbps(高速模式) | 低速设备(传感器、EEPROM) | 引脚少(2线)成本低 | 带宽低距离短 |

| SPI | 主从式 | 单端同步双向串行全双工 | 50Mbps+ | 高速片外通信(Flash,ADC) | 全双工灵活性高 | 需要较多引脚(4+线) |

| Ethe | 星型 | 差分双向串行单工(HUB)全双工(交换机) | 100Gbps(高速) | 网络通信 | 长距离标准化 | 协议栈复杂延迟较高 |

| JTAG | 串行链式结构 |

单端同步 串行单工 |

1Mbps-50Mbps | Bscan,Flash烧录,安全密钥注入(需加密扩展) | 便于硬件调试引脚少(4线基础)标准化(IEEE 1149.1) | 带宽低不支持热插拔需严格同步时序 |

| UART | 点对点 | 单端异步双向串行双工*单工(RS-485) | 12Mbps | 嵌入式设备调试与日志输出,固件烧录 | 简单易用(2线)无需时钟同步长距离支持(RS485) | 无硬件调试功能需预配波特率 |

*单端/差分:一个Tx/Rx 对由几条传输线组成,一条传输线->单端,两条传输线->差分

*单向/双向:传输线只能发送/接收->单向,即可发送也可接收->双向,类似于信号引脚分类的I/O引脚,传输协议多为双向

*串行/并行: 数据传输方式:一位一位依次传输->串行(类似于单车道), 多位同时传输->并行(类似于多车道)

*单工/半双工/双工:发送方,接受方角色固定,数据只能固定方向传->单工(类似于广播), 数据可双向传输但不能同时->半双工(类似于对讲机),数据可同时双向传输->双工(类似于打电话)

PCIe 多通道-Lane(x1/x4/x8/x16)简介

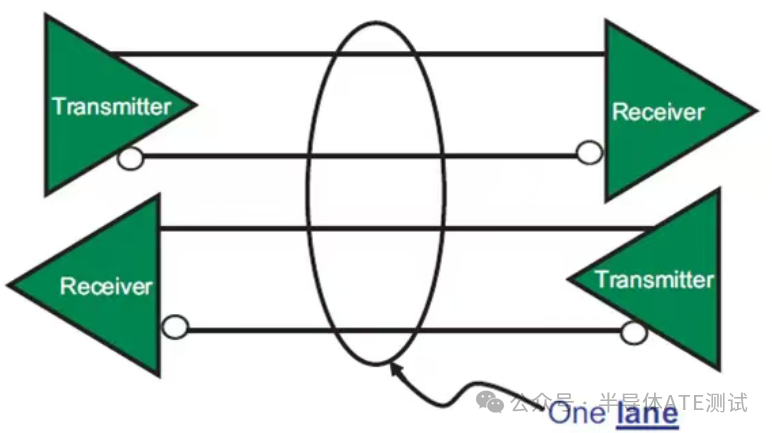

PCIe 通道(lane) x1 = 1对发送(Tx) 差分信号线 + 1对接收(Rx)差分信号线(共四根线)

每个通道独立传输数据,类似高速公路的车道,越多车道,通行能力越强。

通道数越多,总带宽对应成倍增加,以便可适应不同设备通信需求(x1:网卡,x4/x8:SSD, x16:显卡,AI加速卡),通道规格与带宽统计规格如下表所示:

| 通道数 | PCIe Gen3(8 GT/s) | PCIe Gen4(16 GT/s) | PCIe Gen5(32 GT/s) |

| x1 | ≈ 1 GB/s | ≈ 2 GB/s | ≈ 4 GB/s |

| x4 | ≈ 4 GB/s | ≈ 8 GB/s | ≈ 16 GB/s |

| x8 | ≈ 8 GB/s | ≈ 16 GB/s | ≈ 32 GB/s |

| x16 | ≈ 16 GB/s | ≈ 32 GB/s | ≈ 64 GB/s |

注:带宽为双向总带宽(理论值),实际有效带宽约为 97%~98%(扣除编码开销)。

物理接口与兼容性

· 插槽外观:o x16 插槽最长,可兼容 x1/x4/x8 设备(但实际带宽按设备通道数计算)。

o x1 设备 可插入 x16 插槽(物理兼容,但仅使用 1 个通道)。

· 主板支持:

o 主板 PCIe 通道总数由 CPU 或芯片组决定(如 Intel i9 提供 20 条直连通道)

多通道如何工作?

· 数据拆分:发送端将数据分配到多个通道并行传输。o 例如:x16 显卡的帧数据分成 16 份,通过 16 对差分线同时传输。

· 接收端重组:接收端重新合并数据,确保顺序正确。

关于PCIe Lane我们可以做如下Summary:

· x1/x4/x8/x16 = 车道数,越多越快。· 带宽 = 单通道速率 × 通道数(Gen3/4/5 逐代翻倍)。

· 兼容性强:小卡插大槽能用,但带宽按小的算。

“PCIe 通道就像车道——显卡需要 16 车道飙车,SSD 用 4 车道就够了,网卡 1 车道慢慢开。”

从协议原理到物理实现,从ATE测试到PCB设计,PCIe技术的每一个环节都凝聚了工程师们的智慧与匠心。在数据爆炸式增长的时代,PCIe Gen4/Gen5乃至未来的Gen6将持续突破带宽极限,为AI、云计算、自动驾驶等前沿领域提供更强动力。

正如一条高效的高速公路需要精密的规划和维护,PCIe生态的健康发展也离不开协议创新、测试严谨性和设计优化。希望PCIe 接口系列文章能为您提供一份清晰的PCIe技术地图,助您在“数据高速公路”上畅行无阻。未来已来,而PCIe正站在连接万物的技术中心,继续书写速度与可靠性的传奇。